Per aconseguir el béDisseny de PCB, a més del disseny global d’encaminament, les regles d’amplada de línia i espaiament també són crucials. Això és degut a que l'amplada i l'espai de la línia determinen el rendiment i l'estabilitat de la placa de circuit. Per tant, aquest article proporcionarà una introducció detallada a les regles generals de disseny per a l'amplada i l'espai de la línia de PCB.

És important tenir en compte que la configuració predeterminada del programari s’ha de configurar correctament i que l’opció de comprovació de la regla de disseny (DRC) s’ha d’activar abans d’encaminar. Es recomana utilitzar una graella de 5 milions per a l’encaminament i per a la mateixa longitud de longitud igual que es pot establir una xarxa de 1 milió en funció de la situació.

Regles d'amplada de la línia de PCB:

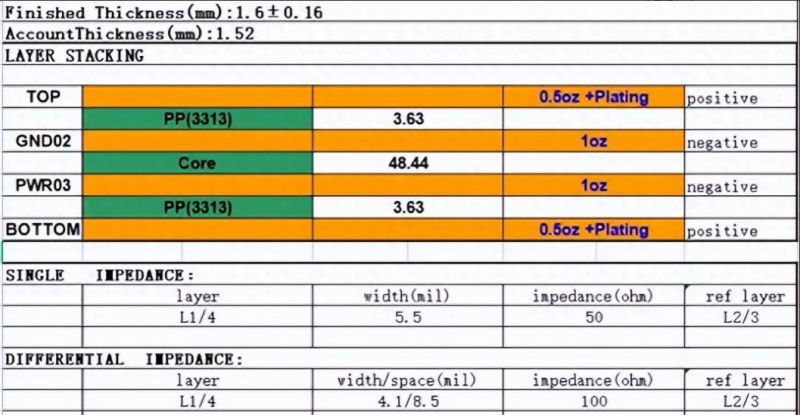

1. El routing hauria de complir primer elCapacitat de fabricacióde la fàbrica. Confirmeu el fabricant de producció amb el client i determineu la seva capacitat de producció. Si el client no proporciona cap requisit específic, consulteu les plantilles de disseny d’impedàncies per a l’amplada de la línia.

2.ImpedànciaPlantilles: Basat en el gruix del tauler proporcionat i els requisits de la capa del client, seleccioneu el model d’impedància adequat. Configureu l'amplada de la línia segons l'amplada calculada dins del model d'impedància. Els valors habituals d’impedància inclouen 50Ω d’un sol termini, diferencial 90Ω, 100Ω, etc. Tingueu en compte si el senyal d’antena de 50ω ha de considerar la referència a la capa contigua. Per a les apilacions de capa de PCB comunes com a referència a continuació.

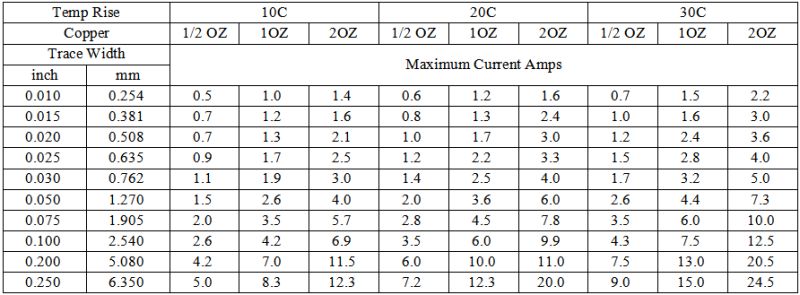

3. Com es mostra al diagrama següent, l'amplada de la línia ha de complir els requisits de capacitat de transport actual. En general, basant -se en l'experiència i en la consideració dels marges d'encaminament, el disseny d'amplada de la línia elèctrica es pot determinar mitjançant les següents directrius: per a un augment de temperatura de 10 ° C, amb un gruix de coure d'1 oz, una amplada de línia de 20 milions pot gestionar un corrent de sobrecàrrega d'1A; Per a un gruix de coure de 0,5 oz, una amplada de la línia de 40 milions pot gestionar un corrent de sobrecàrrega de 1A.

.Fabricants de PCB. Per a dissenys on no sigui necessari el control d’impedàncies (majoritàriament taulers de dues capes), dissenyar una amplada de línia per sobre dels 8 milions pot ajudar a reduir el cost de fabricació del PCB.

5. Considereu elGruix de coureConfiguració de la capa corresponent a l'encaminament. Agafeu el coure de 2 oz, per exemple, intenteu dissenyar l'amplada de la línia per sobre dels 6 milions. Com més gruixut sigui el coure, més ampla l’amplada de la línia. Demaneu els requisits de fabricació de la fàbrica per a dissenys de gruix de coure no estàndard.

6 Per als dissenys BGA amb fosses de 0,5 mm i 0,65 mm, es pot utilitzar una amplada de línia de 3,5 milions en determinades àrees (es pot controlar per regles de disseny).

7. Junta d’IDIEls dissenys poden utilitzar una amplada de la línia de 3mil. Per a dissenys amb amplades de línia inferiors a 3 milions, és necessari confirmar la capacitat de producció de la fàbrica amb el client, ja que alguns fabricants només poden ser capaços d’amplada de 2 milions de línies (es pot controlar per regles de disseny). Les amplades de la línia més fina augmenten els costos de fabricació i amplien el cicle de producció.

8. Els senyals analògics (com ara senyals d’àudio i vídeo) s’han de dissenyar amb línies més gruixudes, normalment al voltant de 15 quilòmetres. Si l’espai és limitat, l’amplada de la línia s’ha de controlar per sobre dels 8 milions.

9. Els senyals RF s’han de manejar amb línies més gruixudes, en referència a capes adjacents i impedància controlades a 50Ω. Els senyals de RF s’han de processar a les capes exteriors, evitant capes internes i minimitzant l’ús de vias o canvis de capa. Els senyals de RF haurien d’estar envoltats d’un pla de terra, i la capa de referència és preferiblement el coure GND.

Normes d’espai de cablejat de PCB

1. El cablejat hauria de complir primer la capacitat de processament de la fàbrica i l’espai entre la línia hauria de complir la capacitat de producció de la fàbrica, generalment controlada a 4 milles o més. Per als dissenys de BGA amb un espai entre 0,5 mm o 0,65 mm, en algunes zones es pot utilitzar un espai de línia de 3,5 milles. Els dissenys d’IDI poden triar un espai d’espai de 3 milions. Els dissenys inferiors a 3 milions han de confirmar la capacitat de producció de la fàbrica de fabricació amb el client. Alguns fabricants tenen una capacitat de producció de 2 MIL (controlada en zones de disseny específiques).

2. Abans de dissenyar la regla d’espai de línia, considereu el requisit de gruix del coure del disseny. Durant 1 unça de coure, intenteu mantenir una distància de 4 milles o més i, per a coure de 2 unces, intenteu mantenir una distància de 6 milles o més.

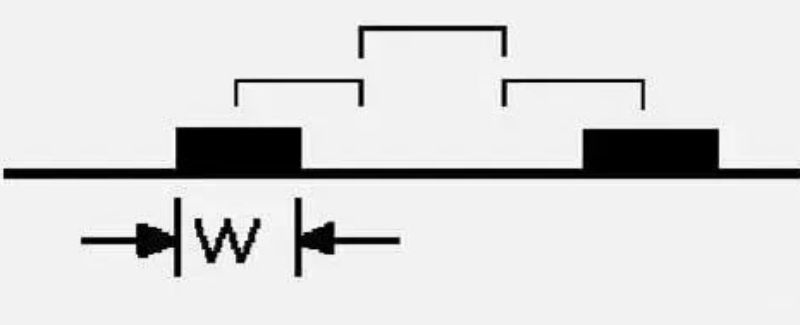

3. El disseny de distància per a parells de senyal diferencial s’ha de definir segons els requisits d’impedància per assegurar un espai adequat.

5. El cablejat s’ha de mantenir allunyat del marc del tauler i intentar assegurar -se que el marc del tauler pot tenir vies de terra (GND). Manteniu la distància entre els senyals i les vores del tauler per sobre dels 40 milions.

5. El senyal de capa de potència ha de tenir una distància d'almenys 10 milles de la capa GND. La distància entre els avions de coure de potència i potència ha de ser almenys 10 milions. Per a alguns ICS (com els BGA) amb espais més reduïts, la distància es pot ajustar adequadament a un mínim de 6 MIL (controlada en zones de disseny específiques).

6. Els senyals importants com els rellotges, diferencials i senyals analògics haurien de tenir una distància de 3 vegades l’amplada (3W) o estar envoltats per avions de terra (GND). La distància entre línies s’ha de mantenir a 3 vegades l’amplada de la línia per reduir la crisi. Si la distància entre els centres de dues línies no és inferior a 3 vegades l'amplada de la línia, pot mantenir el 70% del camp elèctric entre les línies sense interferències, que es coneix com a principi 3W.

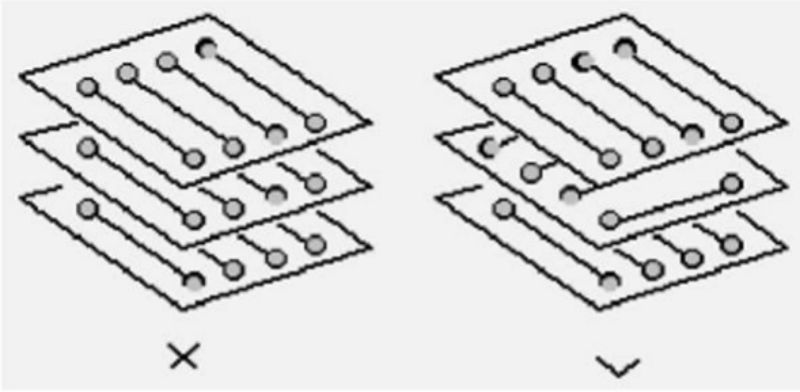

7. Els senyals de capa adjacents han d’evitar el cablejat paral·lel. La direcció d'encaminament ha de formar una estructura ortogonal per reduir la crisi interlayer innecessària.

8. Quan s’encamini a la capa superficial, mantingueu una distància d’almenys 1 mm dels forats de muntatge per evitar circuits curts o esquinçar -se a causa de l’estrès de la instal·lació. La zona al voltant dels forats de cargol s'ha de mantenir clar.

9. Quan dividiu les capes de potència, eviteu les divisions excessivament fragmentades. En un pla de potència, intenteu no tenir més de 5 senyals de potència, preferiblement dins de 3 senyals de potència, per assegurar la capacitat de càrrega actual i evitar el risc de senyalitzar el senyal del pla dividit de les capes adjacents.

10. Les divisions del pla de poder s’han de mantenir el més regular possible, sense divisions llargues ni en forma de manuella, per evitar situacions en què els extrems són grans i el centre és petit. La capacitat de transport actual s’ha de calcular a partir de l’amplada més estreta del pla de coure de potència.

Shenzhen Anke PCB Co., Ltd

2023-9-16

Posada de temps: 19 de setembre de 2013